# Contents

| IV. COMPUTER NETWORKS                                 | 585 |

|-------------------------------------------------------|-----|

| 13. Distributed Algorithms                            | 586 |

| 13.1. Message passing systems and algorithms          | 587 |

| 13.1.1. Modeling message passing systems              | 587 |

| 13.1.2. Asynchronous systems                          | 587 |

| 13.1.3. Synchronous systems                           | 588 |

| 13.2. Basic algorithms                                | 589 |

| 13.2.1. $\operatorname{Broadcast}$                    | 589 |

| 13.2.2. Construction of a spanning tree               | 590 |

| 13.3. Ring algorithms                                 | 594 |

| 13.3.1. The leader election problem                   | 594 |

| 13.3.2. The leader election algorithm                 | 595 |

| 13.3.3. Analysis of the leader election algorithm     | 598 |

| 13.4. Fault-tolerant consensus                        | 601 |

| 13.4.1. The consensus problem                         | 601 |

| 13.4.2. Consensus with crash failures                 | 602 |

| 13.4.3. Consensus with Byzantine failures             | 603 |

| 13.4.4. Lower bound on the ratio of faulty processors | 604 |

| 13.4.5. A polynomial algorithm                        | 604 |

| 13.4.6. Impossibility in asynchronous systems         | 605 |

| 13.5. Logical time, causality, and consistent state   | 606 |

| 13.5.1. Logical time                                  | 607 |

| 13.5.2. Causality                                     | 608 |

| 13.5.3. Consistent state                              | 611 |

| 13.6. Communication services                          | 613 |

| 13.6.1. Properties of broadcast services              | 613 |

| 13.6.2. Ordered broadcast services                    | 615 |

| 13.6.3. Multicast services                            | 619 |

| 13.7. Rumor collection algorithms                     | 620 |

| 13.7.1. Rumor collection problem and requirements     | 620 |

| 13.7.2. Efficient gossip algorithms                   | 621 |

| 13.8. Mutual exclusion in shared memory               | 628 |

# Contents

| 13.8.1. Shared memory systems                       |                                           |     |  |  |  |  |

|-----------------------------------------------------|-------------------------------------------|-----|--|--|--|--|

| 13.8.2.                                             | The mutual exclusion problem              | 628 |  |  |  |  |

| 13.8.3. Mutual exclusion using powerful primitives  |                                           |     |  |  |  |  |

| 13.8.4. Mutual exclusion using read/write registers |                                           |     |  |  |  |  |

| 13.8.5.                                             | Lamport's fast mutual exclusion algorithm | 634 |  |  |  |  |

| Bibliography .                                      |                                           | 638 |  |  |  |  |

| Index                                               |                                           | 640 |  |  |  |  |

| Name Index                                          |                                           | 642 |  |  |  |  |

# **IV. COMPUTER NETWORKS**

# 13. Distributed Algorithms

We define a distributed system as a collection of individual computing devices that can communicate with each other. This definition is very broad, it includes anything, from a VLSI chip, to a tightly coupled multiprocessor, to a local area cluster of workstations, to the Internet. Here we focus on more loosely coupled systems. In a distributed system as we view it, each processor has its semi-independent agenda, but for various reasons, such as sharing of resources, availability, and fault-tolerance, processors need to coordinate their actions.

Distributed systems are highly desirable, but it is notoriously difficult to construct efficient distributed algorithms that perform well in realistic system settings. These difficulties are not just of a more practical nature, they are also fundamental in nature. In particular, many of the difficulties are introduced by the three factors of: asynchrony, limited local knowledge, and failures. Asynchrony means that global time may not be available, and that both absolute and relative times at which events take place at individual computing devices can often not be known precisely. Moreover, each computing device can only be aware of the information it receives, it has therefore an inherently local view of the global status of the system. Finally, computing devices and network components may fail independently, so that some remain functional while others do not.

We will begin by describing the models used to analyse distributed systems in the message-passing model of computation. We present and analyze selected distributed algorithms based on these models. We include a discussion of fault-tolerance in distributed systems and consider several algorithms for reaching agreement in the messages-passing models for settings prone to failures. Given that global time is often unavailable in distributed systems, we present approaches for providing logical time that allows one to reason about causality and consistent states in distributed systems. Moving on to more advanced topics, we present algorithms implementing these services. We also present advanced algorithms for rumor gathering algorithms. Finally, we also consider the mutual exclusion problem in the shared-memory model of distributed computation.

# 13.1. Message passing systems and algorithms

We present our first model of distributed computation, for message passing systems without failures. We consider both synchronous and asynchronous systems and present selected algorithms for message passing systems with arbitrary network topology, and both synchronous and asynchronous settings.

# 13.1.1. Modeling message passing systems

In a message passing system, processors communicate by sending messages over communication channels, where each channel provides a bidirectional connection between two specific processors. We call the pattern of connections described by the channels, the **topology** of the system. This topology is represented by an undirected graph, where each node represents a processor, and an edge is present between two nodes if and only if there is a channel between the two processors represented by the nodes. The collection of channels is also called the **network**. An algorithm for such a message passing system with a specific topology consists of a local program for each processor in the system. This local program provides the ability to the processor to perform local computations, to send and receive messages from each of its neighbours in the given topology.

Each processor in the system is modeled as a possibly infinite state machine. A **configuration** is a vector  $C = (q_0, \ldots, q_{n-1})$  where each  $q_i$  is the state of a processor  $p_i$ . Activities that can take place in the system are modeled as *events* (or actions) that describe indivisible system operations. Examples of events include local computation events and delivery events where a processor receives a message. The behaviour of the system over time is modeled as an *execution*, a (finite or infinite) sequence of configurations  $(C_i)$  alternating with events  $(a_i)$ :  $C_0, a_1, C_1, a_2, C_2, \ldots$ Executions must satisfy a variety of conditions that are used to represent the correctness properties, depending on the system being modeled. These conditions can be classified as either safety or liveness conditions. A *safety condition* for a system is a condition that must hold in every finite prefix of any execution of the system. Informally it states that nothing *bad* has happened yet. A *liveness condition* is a condition that must hold a certain (possibly infinite) number of times. Informally it states that eventually something good must happen. An important liveness condition is *fairness*, which requires that an (infinite) execution contains infinitely many actions by a processor, unless after some configuration no actions are enabled at that processor.

## 13.1.2. Asynchronous systems

We say that a system is *asynchronous* if there is no fixed upper bound on how long it takes for a message to be delivered or how much time elapses between consecutive steps of a processor. An obvious example of such an asynchronous system is the Internet. In an implementation of a distributed system there are often upper bounds on message delays and processor step times. But since these upper bounds are often very large and can change over time, it is often desirable to develop an algorithm that is independent of any timing parameters, that is, an asynchronous algorithm.

In the asynchronous model we say that an execution is *admissible* if each processor has an infinite number of computation events, and every message sent is eventually delivered. The first of these requirements models the fact that processors do not fail. (It does not mean that a processor's local program contains an infinite loop. An algorithm can still terminate by having a transition function not change a processors state after a certain point.)

We assume that each processor's set of states includes a subset of *terminated* states. Once a processor enters such a state it remains in it. The algorithm has *terminated* if all processors are in terminated states and no messages are in transit.

The *message complexity* of an algorithm in the asynchronous model is the maximum over all admissible executions of the algorithm, of the total number of (point-to-point) messages sent.

A *timed execution* is an execution that has a nonnegative real number associated with each event, the *time* at which the event occurs. To measure the *time complexity* of an asynchronous algorithm we first assume that the maximum message delay in any execution is one unit of time. Hence the *time complexity* is the maximum time until termination among all timed admissible executions in which every message delay is at most one. Intuitively this can be viewed as taking any execution of the algorithm and normalising it in such a way that the longest message delay becomes one unit of time.

#### 13.1.3. Synchronous systems

In the synchronous model processors execute in lock-step. The execution is partitioned into rounds so that every processor can send a message to each neighbour, the messages are delivered, and every processor computes based on the messages just received. This model is very convenient for designing algorithms. Algorithms designed in this model can in many cases be automatically simulated to work in other, more realistic timing models.

In the synchronous model we say that an execution is admissible if it is infinite. From the round structure it follows then that every processor takes an infinite number of computation steps and that every message sent is eventually delivered. Hence in a synchronous system with no failures, once a (deterministic) algorithm has been fixed, the only relevant aspect determining an execution that can change is the initial configuration. On the other hand in an asynchronous system, there can be many different executions of the same algorithm, even with the same initial configuration and no failures, since here the interleaving of processor steps, and the message delays, are not fixed.

The notion of *terminated states* and the *termination* of the algorithm is defined in the same way as in the asynchronous model.

The *message complexity* of an algorithm in the synchronous model is the maximum over all admissible executions of the algorithm, of the total number of messages sent.

To measure time in a synchronous system we simply count the number of rounds until termination. Hence the *time complexity* of an algorithm in the synchronous model is the maximum number of rounds in any admissible execution of the algorithm until the algorithm has terminated.

# 13.2. Basic algorithms

We begin with some simple examples of algorithms in the message passing model.

# 13.2.1. Broadcast

We start with a simple algorithm SPANNING-TREE-BROADCAST for the (single message) broadcast problem, assuming that a spanning tree of the network graph with nnodes (processors) is already given. Later, we will remove this assumption. A processor  $p_i$  wishes to send a message M to all other processors. The spanning tree rooted at  $p_i$  is maintained in a distributed fashion: Each processor has a distinguished channel that leads to its *parent* in the tree as well as a set of channels that lead to its *children* in the tree. The root  $p_i$  sends the message M on all channels leading to its children. When a processor receives the message on a channel from its parent, it sends M on all channels leading to its children.

```

Spanning-Tree-Broadcast

```

Initially M is in transit from  $p_i$  to all its children in the spanning tree. Code for  $p_i$ :

```

1 upon receiving no message: // first computation event by p_i

```

```

2 terminate

```

Code for  $p_i$ ,  $0 \le j \le n-1$ ,  $j \ne i$ :

- 3 upon receiving M from parent:

- 4 send M to all children

- 5 terminate

The algorithm SPANNING-TREE-BROADCAST is correct whether the system is synchronous or asynchronous. Moreover, the message and time complexities are the same in both models.

Using simple inductive arguments we will first prove a lemma that shows that by the end of round t, the message M reaches all processors at distance t (or less) from  $p_r$  in the spanning tree.

**Lemma 13.1** In every admissible execution of the broadcast algorithm in the synchronous model, every processor at distance t from  $p_r$  in the spanning tree receives the message M in round t.

**Proof** We proceed by induction on the distance t of a processor from  $p_r$ . First let t = 1. It follows from the algorithm that each child of  $p_r$  receives the message in round 1.

Assume that each processor at distance t - 1 received the message M in round

t-1. We need to show that each processor  $p_t$  at distance t receives the message in round t. Let  $p_s$  be the parent of  $p_t$  in the spanning tree. Since  $p_s$  is at distance t-1 from  $p_r$ , by the induction hypothesis,  $p_s$  received M in round t-1. By the algorithm,  $p_t$  will hence receive M in round t.

By Lemma 13.1 the time complexity of the broadcast algorithm is d, where d is the depth of the spanning tree. Now since d is at most n - 1 (when the spanning tree is a chain) we have:

**Theorem 13.2** There is a synchronous broadcast algorithm for n processors with message complexity n - 1 and time complexity d, when a rooted spanning tree with depth d is known in advance.

We now move to an asynchronous system and apply a similar analysis.

**Lemma 13.3** In every admissible execution of the broadcast algorithm in the asynchronous model, every processor at distance t from  $p_r$  in the spanning tree receives the message M by time t.

**Proof** We proceed by induction on the distance t of a processor from  $p_r$ . First let t = 1. It follows from the algorithm that M is initially in transit to each processor  $p_i$  at distance 1 from  $p_r$ . By the definition of time complexity for the asynchronous model,  $p_i$  receives M by time 1.

Assume that each processor at distance t - 1 received the message M at time t - 1. We need to show that each processor  $p_t$  at distance t receives the message by time t. Let  $p_s$  be the parent of  $p_t$  in the spanning tree. Since  $p_s$  is at distance t - 1 from  $p_r$ , by the induction hypothesis,  $p_s$  sends M to  $p_t$  when it receives M at time t - 1. By the algorithm,  $p_t$  will hence receive M by time t.

We immediately obtain:

**Theorem 13.4** There is an asynchronous broadcast algorithm for n processors with message complexity n - 1 and time complexity d, when a rooted spanning tree with depth d is known in advance.

# 13.2.2. Construction of a spanning tree

The asynchronous algorithm called FLOOD, discussed next, constructs a spanning tree rooted at a designated processor  $p_r$ . The algorithm is similar to the Depth First Search (DFS) algorithm. However, unlike DFS where there is just one processor with "global knowledge" about the graph, in the FLOOD algorithm, each processor has "local knowledge" about the graph, processors coordinate their work by exchanging messages, and processors and messages may get delayed arbitrarily. This makes the design and analysis of FLOOD algorithm challenging, because we need to show that the algorithm indeed constructs a spanning tree despite conspiratorial selection of these delays.

#### 13.2. Basic algorithms

**Algorithm description.** Each processor has four local variables. The links adjacent to a processor are identified with distinct numbers starting from 1 and stored in a local variable called *neighbours*. We will say that the *spanning tree* has been constructed. when the variable parent stores the identifier of the link leading to the parent of the processor in the spanning tree, except that this variable is NONE for the designated processor  $p_r$ ; children is a set of identifiers of the links leading to the children processors in the tree; and other is a set of identifiers of all other links. So the knowledge about the spanning tree may be "distributed" across processors.

The code of each processor is composed of segments. There is a segment (lines 1–4) that describes how local variables of a processor are initialised. Recall that the local variables are initialised that way before time 0. The next three segments (lines 5–11, 12–15 and 16–19) describe the instructions that any processor executes in response to having received a message:  $\langle adopt \rangle$ ,  $\langle approved \rangle$  or  $\langle rejected \rangle$ . The last segment (lines 20–22) is only included in the code of processor  $p_r$ . This segment is executed only when the local variable *parent* of processor  $p_r$  is NIL. At some point of time, it may happen that more than one segment can be executed by a processor (e.g., because the processor received  $\langle adopt \rangle$  messages from two processors). Then the processor executes the segments serially, one by one (segments of any given processor are never executed during an execution. Every message that can be processed is eventually processed and every segment that can be executed is eventually executed (fairness).

#### FLOOD

```

Code for any processor p_k, 1 \le k \le n

initialisation

1

2

parent \leftarrow NIL

3

children \leftarrow \emptyset

4

other \leftarrow \emptyset

process message \langle adopt \rangle that has arrived on link j

5

6

if parent = NIL

7

then parent \leftarrow j

8

send \langle approved \rangle to link j

send \langle adopt \rangle to all links in neighbours \setminus \{j\}

9

10

else send < rejected > to link j

11

process message \langle approved \rangle that has arrived on link j

12

children \leftarrow children \cup \{j\}

```

```

13 if children \cup other = neighbours \setminus \{parent\}

```

```

14 then terminate

```

```

15 process message \langle rejected \rangle that has arrived on link j

```

```

16 other \leftarrow other \cup \{j\}

```

```

17 if children \cup other = neighbours \setminus \{parent\}

```

```

18 then terminate

```

Extra code for the designated processor  $p_r$

```

19 if parent = NIL

```

```

20 then parent \leftarrow NONE

```

```

21 send \langle adopt \rangle to all links in neighbours

```

Let us outline how the algorithm works. The designated processor sends an  $\langle adopt \rangle$  message to all its neighbours, and assigns NONE to the *parent* variable (NIL and NONE are two distinguished values, different from any natural number), so that it never again sends the message to any neighbour.

When a processor processes message  $\langle adopt \rangle$  for the first time, the processor assigns to its own *parent* variable the identifier of the link on which the message has arrived, responds with an  $\langle approved \rangle$  message to that link, and forwards an  $\langle adopt \rangle$  message to every other link. However, when a processor processes message  $\langle adopt \rangle$  again, then the processor responds with a  $\langle rejected \rangle$  message, because the *parent* variable is no longer NIL.

When a processor processes message  $\langle approved \rangle$ , it adds the identifier of the link on which the message has arrived to the set *children*. It may turn out that the sets *children* and *other* combined form identifiers of all links adjacent to the processor except for the identifier stored in the *parent* variable. In this case the processor enters a terminating state.

When a processor processes message  $\langle rejected \rangle$ , the identifier of the link is added to the set *other*. Again, when the union of *children* and *other* is large enough, the processor enters a terminating state.

**Correctness proof.** We now argue that FLOOD constructs a spanning tree. The key moments in the execution of the algorithm are when any processor assigns a value to its *parent* variable. These assignments determine the "shape" of the spanning tree. The facts that any processor eventually executes an instruction, any message is eventually delivered, and any message is eventually processed, ensure that the knowledge about these assignments spreads to neighbours. Thus the algorithm is expanding a subtree of the graph, albeit the expansion may be slow. Eventually, a spanning tree is formed. Once a spanning tree has been constructed, eventually every processor will terminate, even though some processors may have terminated even before the spanning tree has been constructed.

**Lemma 13.5** For any  $1 \le k \le n$ , there is time  $t_k$  which is the first moment when there are exactly k processors whose parent variables are not NIL, and these processors and their parent variables form a tree rooted at  $p_r$ .

**Proof** We prove the statement of the lemma by induction on k. For the base case, assume that k = 1. Observe that processor  $p_r$  eventually assigns NONE to its *parent*

variable. Let  $t_1$  be the moment when this assignment happens. At that time, the *parent* variable of any processor other than  $p_r$  is still NIL, because no  $\langle adopt \rangle$  messages have been sent so far. Processor  $p_r$  and its *parent* variable form a tree with a single node and not arcs. Hence they form a rooted tree. Thus the inductive hypothesis holds for k = 1.

For the inductive step, suppose that  $1 \le k < n$  and that the inductive hypothesis holds for k. Consider the time  $t_k$  which is the first moment when there are exactly k processors whose *parent* variables are not nil. Because k < n, there is a non-tree processor. But the graph G is connected, so there is a non-tree processor adjacent to the tree. (For any subset T of processors, a processor  $p_i$  is **adjacent** to T if and only if there an edge in the graph G from  $p_i$  to a processor in T.) Recall that by definition, *parent* variable of such processor is NIL. By the inductive hypothesis, the k processors must have executed line 7 of their code, and so each either has already sent or will eventually send  $\langle adopt \rangle$  message to all its neighbours on links other than the *parent* link. So the non-tree processors adjacent to the tree have already received or will eventually receive  $\langle adopt \rangle$  messages. Eventually, each of these adjacent processors will, therefore, assign a value other than NIL to its *parent* variable. Let  $t_{k+1} > t_k$  be the first moment when any processor performs such assignment, and let us denote this processor by  $p_i$ . This cannot be a tree processor, because such processor never again assigns any value to its *parent* variable. Could  $p_i$  be a non-tree processor that is not adjacent to the tree? It could not, because such processor does not have a direct link to a tree processor, so it cannot receive  $\langle adopt \rangle$  directly from the tree, and so this would mean that at some time t' between  $t_k$  and  $t_{k+1}$  some other nontree processor  $p_j$  must have sent  $\langle adopt \rangle$  message to  $p_i$ , and so  $p_j$  would have to assign a value other than NIL to its *parent* variable some time after  $t_k$  but before  $t_{k+1}$ , contradicting the fact the  $t_{k+1}$  is the first such moment. Consequently,  $p_i$  is a non-tree processor adjacent to the tree, such that, at time  $t_{k+1}$ ,  $p_i$  assigns to its *parent* variable the index of a link leading to a tree processor. Therefore, time  $t_{k+1}$ is the first moment when there are exactly k + 1 processors whose *parent* variables are not NIL, and, at that time, these processors and their *parent* variables form a tree rooted at  $p_r$ . This completes the inductive step, and the proof of the lemma.

**Theorem 13.6** Eventually each processor terminates, and when every processor has terminated, the subgraph induced by the parent variables forms a spanning tree rooted at  $p_r$ .

**Proof** By Lemma 13.5, we know that there is a moment  $t_n$  which is the first moment when all processors and their *parent* variables form a spanning tree.

Is it possible that every processor has terminated before time  $t_n$ ? By inspecting the code, we see that a processor terminates only after it has received  $\langle rejected \rangle$ or  $\langle approved \rangle$  messages from all its neighbours other than the one to which *parent* link leads. A processor receives such messages only in response to  $\langle adopt \rangle$  messages that the processor sends. At time  $t_n$ , there is a processor that still has not even sent  $\langle adopt \rangle$  messages. Hence, not every processor has terminated by time  $t_n$ .

Will every processor eventually terminate? We notice that by time  $t_n$ , each processor either has already sent or will eventually send  $\langle adopt \rangle$  message to all

its neighbours other than the one to which *parent* link leads. Whenever a processor receives  $\langle adopt \rangle$  message, the processor responds with  $\langle rejected \rangle$  or  $\langle approved \rangle$ , even if the processor has already terminated. Hence, eventually, each processor will receive either  $\langle rejected \rangle$  or  $\langle approved \rangle$  message on each link to which the processor has sent  $\langle adopt \rangle$  message. Thus, eventually, each processor terminates.

We note that the fact that a processor has terminated does not mean that a spanning tree has already been constructed. In fact, it may happen that processors in a different part of the network have not even received any message, let alone terminated.

**Theorem 13.7** Message complexity of FLOOD is O(e), where e is the number of edges in the graph G.

The proof of this theorem is left as Problem 13-1.

### **Exercises**

**13.2-1** It may happen that a processor has terminated even though a processor has not even received any message. Show a simple network and how to delay message delivery and processor computation to demonstrate that this can indeed happen.

**13.2-2** It may happen that a processor has terminated but may still respond to a message. Show a simple network and how to delay message delivery and processor computation to demonstrate that this can indeed happen.

# 13.3. Ring algorithms

One often needs to coordinate the activities of processors in a distributed system. This can frequently be simplified when there is a single processor that acts as a coordinator. Initially, the system may not have any coordinator, or an existing coordinator may fail and so another may need to be elected. This creates the problem where processors must elect exactly one among them, a *leader*. In this section we study the problem for special types of networks—rings. We will develop an asynchronous algorithm for the problem. As we shall demonstrate, the algorithm has asymptotically optimal message complexity. In the current section, we will see a distributed analogue of the well-known divide-and-conquer technique often used in sequential algorithms to keep their time complexity low. The technique used in distributed systems helps reduce the message complexity.

# 13.3.1. The leader election problem

The leader election problem is to elect exactly leader among a set of processors. Formally each processor has a local variable *leader* initially equal to NIL. An algorithm is said to *solve the leader election problem* if it satisfies the following conditions:

1. in any execution, exactly one processor eventually assigns TRUE to its *leader*

#### 13.3. Ring algorithms

variable, all other processors eventually assign  ${\tt FALSE}$  to their leader variables, and

2. in any execution, once a processor has assigned a value to its *leader* variable, the variable remains unchanged.

**Ring model.** We study the leader election problem on a special type of network the ring. Formally, the graph G that models a distributed system consists of n nodes that form a simple cycle; no other edges exist in the graph. The two links adjacent to a processor are labeled CW (Clock-Wise) and CCW (Counter Clock-Wise). Processors agree on the orientation of the ring i.e., if a message is passed on in CW direction n times, then it visits all n processors and comes back to the one that initially sent the message; same for CCW direction. Each processor has a unique *identifier* that is a natural number, i.e., the identifier of each processor is different from the identifier of any other processor; the identifiers do not have to be consecutive numbers  $1, \ldots, n$ . Initially, no processor knows the identifier of any other processor. Also processors do not know the size n of the ring.

## 13.3.2. The leader election algorithm

BULLY elects a leader among asynchronous processors  $p_1, \ldots, p_n$ . Identifiers of processors are used by the algorithm in a crucial way. Briefly speaking, each processor tries to become the leader, the processor that has the largest identifier among all processors blocks the attempts of other processors, declares itself to be the leader, and forces others to declare themselves not to be leaders.

Let us begin with a simpler version of the algorithm to exemplify some of the ideas of the algorithm. Suppose that each processor sends a message around the ring containing the identifier of the processor. Any processor passes on such message only if the identifier that the message carries is strictly larger than the identifier of the processor. Thus the message sent by the processor that has the largest identifier among the processors of the ring, will always be passed on, and so it will eventually travel around the ring and come back to the processor that initially sent it. The processor can detect that such message has come back, because no other processor sends a message with this identifier (identifiers are distinct). We observe that, no other message will make it all around the ring, because the processor with the largest identifier will not pass it on. We could say that the processor with the largest identifier "swallows" these messages that carry smaller identifiers. Then the processor becomes the leader and sends a special message around the ring forcing all others to decide not to be leaders. The algorithm has  $\Theta(n^2)$  message complexity, because each processor induces at most n messages, and the leader induces n extra messages; and one can assign identifiers to processors and delay processors and messages in such a way that the messages sent by a constant fraction of n processors are passed on around the ring for a constant fraction of n hops. The algorithm can be improved so as to reduce message complexity to  $O(n \lg n)$ , and such improved algorithm will be presented in the remainder of the section.

The key idea of the BULLY algorithm is to make sure that not too many mes-

sages travel far, which will ensure  $O(n \lg n)$  message complexity. Specifically, the activity of any processor is divided into phases. At the beginning of a phase, a processor sends "probe" messages in both directions: CW and CCW. These messages carry the identifier of the sender and a certain "time-to-live" value that limits the number of hops that each message can make. The probe message may be passed on by a processor provided that the identifier carried by the message is larger than the identifier of the processor. When the message reaches the limit, and has not been swallowed, then it is "bounced back". Hence when the initial sender receives two bounced back messages, each from each direction, then the processor is certain that there is no processor with larger identifier up until the limit in CW nor CCW directions, because otherwise such processor would swallow a probe message. Only then does the processor enter the next phase through sending probe messages again, this time with the time-to-live value increased by a factor, in an attempt to find if there is no processor with a larger identifier in twice as large neighbourhood. As a result, a probe message that the processor sends will make many hops only when there is no processor with larger identifier in a large neighbourhood of the processor. Therefore, fewer and fewer processors send messages that can travel longer and longer distances. Consequently, as we will soon argue in detail, message complexity of the algorithm is  $O(n \lg n)$ .

We detail the BULLY algorithm. Each processor has five local variables. The variable *id* stores the unique identifier of the processor. The variable *leader* stores TRUE when the processor decides to be the leader, and FALSE when it decides not to be the leader. The remaining three variables are used for bookkeeping: *asleep* determines if the processor has ever sent a < probe, id, 0, 0 > message that carries the identifier *id* of the processor. Any processor may send  $< probe, id, phase, 2^{phase-1} >$  message in both directions (CW and CCW) for different values of *phase*. Each time a message is sent, a < reply, id, phase > message may be sent back to the processor. The variables *CWreplied* and *CCWreplied* are used to remember whether the replies have already been processed the processor.

The code of each processor is composed of five segments. The first segment (lines 1–5) initialises the local variables of the processor. The second segment (lines 6–8) can only be executed when the local variable *asleep* is TRUE. The remaining three segments (lines 9–17, 1–26, and 27–31) describe the actions that the processor takes when it processes each of the three types of messages: < probe, ids, phase, ttl>, < reply, ids, phase> and < terminate> respectively. The messages carry parameters ids, phase and ttl that are natural numbers.

We now describe how the algorithm works. Recall that we assume that the local variables of each processor have been initialised before time 0 of the global clock. Each processor eventually sends a  $\langle probe, id, 0, 0 \rangle$  message carrying the identifier *id* of the processor. At that time we say that the processor *enters* phase number zero. In general, when a processor sends a message  $\langle probe, id, phase, 2^{phase} - 1 \rangle$ , we say that the processor *enters* phase number *phase*. Message  $\langle probe, id, 0, 0 \rangle$  is never sent again because FALSE is assigned to *asleep* in line 7. It may happen that by the time this message is sent, some other messages have already been processed by the processor.

When a processor processes message  $\langle probe, ids, phase, ttl \rangle$  that has arrived on

#### 13.3. Ring algorithms

link CW (the link leading in the clock-wise direction), then the actions depend on the relationship between the parameter ids and the identifier id of the processor. If ids is smaller than id, then the processor does nothing else (the processor swallows the message). If ids is equal to id and processor has not yet decided, then, as we shall see, the probe message that the processor sent has circulated around the entire ring. Then the processor sends a  $\langle terminate \rangle$  message, decides to be the leader, and terminates (the processor may still process messages after termination). If idsis larger than id, then actions of the processor depend on the value of the parameter ttl (time-to-live). When the value is strictly larger than zero, then the processor passes on the probe message with ttl decreased by one. If, however, the value of ttl is already zero, then the processor sends back (in the CW direction) a reply message. Symmetric actions are executed when the  $\langle probe, ids, phase, ttl \rangle$  message has arrived on link CCW, in the sense that the directions of sending messages are respectively reversed – see the code for details.

#### BULLY

```

Code for any processor p_k, 1 \le k \le n

initialisation

1

2

asleep \leftarrow \text{TRUE}

3

CWreplied \leftarrow FALSE

4

CCWreplied \leftarrow FALSE

5

leader \leftarrow \text{NIL}

if asleep

6

7

then asleep \leftarrow FALSE

8

send < probe, id, 0, 0 > to links CW and CCW

9

process message < probe, ids, phase, ttl> that has arrived

on link CW (resp. CCW)

10

if id = ids and leader = NIL

then send <terminate> to link CCW

11

12

leader \leftarrow TRUE

13

terminate

14

if ids > id and ttl > 0

15

then send < probe, ids, phase, ttl - 1 >

to link CCW (resp. CW)

16

if ids > id and ttl = 0

17

then send <reply,ids,phase> to link CW (resp. CCW)

```

18 process message  $\langle reply, ids, phase \rangle$  that has arrived on link CW (resp. CCW) 19 if  $id \neq ids$

- 20 **then send** <*reply,ids,phase>* to link CCW (resp. CW)

- 21 **else**  $CWreplied \leftarrow TRUE$  (resp. CCWreplied)

- 22 **if** *CWreplied* and *CCWreplied*

- 23 **then**  $CWreplied \leftarrow FALSE$

- 24  $CCWreplied \leftarrow FALSE$

- 25 send  $< probe, id, phase + 1, 2^{phase + 1} 1 >$

- to links CW and CCW

| 26 | process message | < terminate > | that | has | arrived | on | link C | W |

|----|-----------------|---------------|------|-----|---------|----|--------|---|

| 97 | f loador NII    |               |      |     |         |    |        |   |

- 27 **if** leader NIL

- 28 **then send** <*terminate*> to link CCW

- 29  $leader \leftarrow False$

```

30 terminate

```

When a processor processes message  $\langle reply, ids, phase \rangle$  that has arrived on link CW, then the processor first checks if *ids* is different from the identifier *id* of the processor. If so, the processor merely passes on the message. However, if *ids* = *id*, then the processor records the fact that a reply has been received from direction CW, by assigning TRUE to *CWreplied*. Next the processor checks if both *CWreplied* and *CCWreplied* variables are *true*. If so, the processor has received replies from both directions. Then the processor assigns *false* to both variables. Next the processor, the next phase number *phase* + 1, and an increased time-to-live parameter  $2^{phase+1} - 1$ . Symmetric actions are executed when  $\langle reply, ids, phase \rangle$  has arrived on link CCW.

The last type of message that a processor can process is  $\langle terminate \rangle$ . The processor checks if it has already decided to be or not to be the leader. When no decision has been made so far, the processor passes on the  $\langle terminate \rangle$  message and decides not to be the leader. This message eventually reaches a processor that has already decided, and then the message is no longer passed on.

# 13.3.3. Analysis of the leader election algorithm

We begin the analysis by showing that the algorithm BULLY solves the leader election problem.

**Theorem 13.8** BULLY solves the leader election problem on any ring with asynchronous processors.

**Proof** We need to show that the two conditions listed at the beginning of the section are satisfied. The key idea that simplifies the argument is to focus on one processor. Consider the processor  $p_i$  with maximum *id* among all processors in the ring. This processor eventually executes lines 6–8. Then the processor sends < probe, id, 0, 0 > messages in CW and CCW directions. Note that whenever the processor sends  $< probe, id, phase, 2^{phase} - 1 >$  messages, each such message is always passed on by

#### 13.3. Ring algorithms

other processors, until the *ttl* parameter of the message drops down to zero, or the message travels around the entire ring and arrives at  $p_i$ . If the message never arrives at  $p_i$ , then a processor eventually receives the probe message with ttl equal to zero, and the processor sends a response back to  $p_i$ . Then, eventually  $p_i$  receives messages  $\langle reply, id, phase \rangle$  from each directions, and enters phase number phase + 1 by sending probe messages  $\langle probe, id, phase+1, 2^{phase+1} - 1 \rangle$  in both directions. These messages carry a larger time-to-live value compared to the value from the previous phase number *phase*. Since the ring is finite, eventually *ttl* becomes so large that processor  $p_i$  receives a probe message that carries the identifier of  $p_i$ . Note that  $p_i$ will eventually receive two such messages. The first time when  $p_i$  processes such message, the processor sends a  $\langle terminate \rangle$  message and terminates as the leader. The second time when  $p_i$  processes such message, lines 11–13 are not executed, because variable *leader* is no longer NIL. Note that no other processor  $p_i$  can execute lines 11–13, because a probe message originated at  $p_i$  cannot travel around the entire ring, since  $p_i$  is on the way, and  $p_i$  would swallow the message; and since identifiers are distinct, no other processor sends a probe message that carries the identifier of processor  $p_i$ . Thus no processor other than  $p_i$  can assign TRUE to its *leader* variable. Any processor other than  $p_i$  will receive the *<terminate>* message, assign FALSE to its *leader* variable, and pass on the message. Finally, the *<terminate>* message will arrive at  $p_i$ , and  $p_i$  will not pass it anymore. The argument presented thus far ensures that eventually exactly one processor assigns TRUE to its *leader* variable, all other processors assign FALSE to their *leader* variables, and once a processor has assigned a value to its *leader* variable, the variable remains unchanged.

Our next task is to give an upper bound on the number of messages sent by the algorithm. The subsequent lemma shows that the number of processors that can enter a phase decays exponentially as the phase number increases.

# **Lemma 13.9** Given a ring of size n, the number k of processors that enter phase number $i \ge 0$ is at most $n/2^{i-1}$ .

**Proof** There are exactly *n* processors that enter phase number i = 0, because each processor eventually sends < probe, id, 0, 0 > message. The bound stated in the lemma says that the number of processors that enter phase 0 is at most 2n, so the bound evidently holds for i = 0. Let us consider any of the remaining cases i.e., let us assume that  $i \geq 1$ . Suppose that a processor  $p_i$  enters phase number i, and so by definition it sends message  $\langle probe, id, i, 2^i - 1 \rangle$ . In order for a processor to send such message, each of the two probe messages  $< probe, id, i-1, 2^{i-1} - 1 >$  that the processor sent in the previous phase in both directions must have made  $2^{i-1}$  hops always arriving at a processor with strictly lower identifier than the identifier of  $p_i$  (because otherwise, if a probe message arrives at a processor with strictly larger or the same identifier, than the message is swallowed, and so a reply message is not generated, and consequently  $p_i$  cannot enter phase number i). As a result, if a processor enters phase number i, then there is no other processor  $2^{i-1}$  hops away in both directions that can ever enter the phase. Suppose that there are  $k \ge 1$  processors that enter phase *i*. We can associate with each such processor  $p_i$ , the  $2^{i-1}$  consecutive processors that follow  $p_i$  in the CW direction. This association assigns  $2^{i-1}$  distinct processors to each of the k processors. So there must be at least  $k + k \cdot 2^{i-1}$  distinct processor in the ring. Hence  $k(1+2^{i-1}) \leq n$ , and so we can weaken this bound by dropping 1, and conclude that  $k \cdot 2^{i-1} \leq n$ , as desired.

**Theorem 13.10** The algorithm BULLY has  $O(n \lg n)$  message complexity, where n is the size of the ring.

**Proof** Note that any processor in phase i, sends messages that are intended to travel  $2^i$  away and back in each direction (CW and CCW). This contributes at most  $4 \cdot 2^i$  messages per processor that enters phase number i. The contribution may be smaller than  $4 \cdot 2^i$  if a probe message gets swallowed on the way away from the processor. Lemma 13.9 provides an upper bound on the number of processors that enter phase number k. What is the highest phase that a processor can ever enter? The number k of processors that can be in phase i is at most  $n/2^{i-1}$ . So when  $n/2^{i-1} < 1$ , then there can be no processor that ever enters phase i. Thus no processor can enter any phase beyond phase number  $h = 1 + \lceil \log_2 n \rceil$ , because  $n < 2^{(h+1)-1}$ . Finally, a single processor sends one termination message that travels around the ring once. So for the total number of messages sent by the algorithm we get the

$$n + \sum_{i=0}^{1+\lceil \log_2 n \rceil} \left( n/2^{i-1} \cdot 4 \cdot 2^i \right) = n + \sum_{i=0}^{1+\lceil \log_2 n \rceil} 8n = O(n \lg n)$$

upper bound.

Burns furthermore showed that the asynchronous leader election algorithm is asymptotically optimal: Any uniform algorithm solving the leader election problem in an asynchronous ring must send the number of messages at least proportional to  $n \lg n$ .

**Theorem 13.11** Any uniform algorithm for electing a leader in an asynchronous ring sends  $\Omega(n \lg n)$  messages.

The proof, for any algorithm, is based on constructing certain executions of the algorithm on rings of size n/2. Then two rings of size n/2 are pasted together in such a way that the constructed executions on the smaller rings are combined, and  $\Theta(n)$  additional messages are received. This construction strategy yields the desired logarithmic multiplicative overhead.

## Exercises

**13.3-1** Show that the simplified BULLY algorithm has  $\Omega(n^2)$  message complexity, by appropriately assigning identifiers to processors on a ring of size n, and by determining how to delay processors and messages.

**13.3-2** Show that the algorithm BULLY has  $\Omega(n \lg n)$  message complexity.

#### 13.4. Fault-tolerant consensus

# 13.4. Fault-tolerant consensus

The algorithms presented so far are based on the assumption that the system on which they run is reliable. Here we present selected algorithms for unreliable distributed systems, where the active (or correct) processors need to coordinate their activities based on common decisions.

It is inherently difficult for processors to reach agreement in a distributed setting prone to failures. Consider the deceptively simple problem of two failure-free processors attempting to agree on a common bit using a communication medium where messages may be lost. This problem is known as the *two generals problem*. Here two generals must coordinate an attack using couriers that may be destroyed by the enemy. It turns out that it is not possible to solve this problem using a finite number of messages. We prove this fact by contradiction. Assume that there is a protocol used by processors A and B involving a finite number of messages. Let us consider such a protocol that uses the smallest number of messages, say kmessages. Assume without loss of generality that the last  $k^{th}$  message is sent from A to B. Since this final message is not acknowledged by B, A must determine the decision value whether or not B receives this message. Since the message may be lost, B must determine the decision value without receiving this final message. But now both A and B decide on a common value without needing the  $k^{th}$  message. In other words, there is a protocol that uses only k-1 messages for the problem. But this contradicts the assumption that k is the smallest number of messages needed to solve the problem.

In the rest of this section we consider agreement problems where the communication medium is reliable, but where the processors are subject to two types of failures: *crash failures*, where a processor stops and does not perform any further actions, and *Byzantine failures*, where a processor may exhibit arbitrary, or even malicious, behaviour as the result of the failure.

The algorithms presented deal with the so called *consensus problem*, first introduced by Lamport, Pease, and Shostak. The consensus problem is a fundamental coordination problem that requires processors to agree on a common output, based on their possibly conflicting inputs.

## 13.4.1. The consensus problem

We consider a system in which each processor  $p_i$  has a special state component  $x_i$ , called the *input* and  $y_i$ , called the *output* (also called the *decision*). The variable  $x_i$  initially holds a value from some well ordered set of possible inputs and  $y_i$  is undefined. Once an assignment to  $y_i$  has been made, it is irreversible. Any solution to the consensus problem must guarantee:

- **Termination:** In every admissible execution,  $y_i$  is eventually assigned a value, for every nonfaulty processor  $p_i$ .

- Agreement: In every execution, if  $y_i$  and  $y_j$  are assigned, then  $y_i = y_j$ , for all nonfaulty processors  $p_i$  and  $p_j$ . That is nonfaulty processors do not decide on conflicting values.

• Validity: In every execution, if for some value v,  $x_i = v$  for all processors  $p_i$ , and if  $y_i$  is assigned for some nonfaulty processor  $p_i$ , then  $y_i = v$ . That is, if all processors have the same input value, then any value decided upon must be that common input.

Note that in the case of crash failures this validity condition is equivalent to requiring that every nonfaulty decision value is the input of some processor. Once a processor crashes it is of no interest to the algorithm, and no requirements are put on its decision.

We begin by presenting a simple algorithm for consensus in a synchronous message passing system with crash failures.

# 13.4.2. Consensus with crash failures

Since the system is synchronous, an execution of the system consists of a series of rounds. Each round consists of the delivery of all messages, followed by one computation event for every processor. The set of faulty processors can be different in different executions, that is, it is not known in advance. Let F be a subset of at most f processors, the faulty processors. Each round contains exactly one computation event for the processors not in F and at most one computation event for every processor in F. Moreover, if a processor in F does not have a computation event in some round, it does not have such an event in any further round. In the last round in which a faulty processor has a computation event, an arbitrary subset of its outgoing messages are delivered.

#### CONSENSUS-WITH-CRASH-FAILURES

Code for processor  $p_i$ ,  $0 \le i \le n-1$ . Initially  $V = \{x\}$ round  $k, 1 \le k \le f+1$ **send**  $\{v \in V : p_i \text{ has not already sent } v\}$  to all processors **receive**  $S_j$  from  $p_j, 0 \le j \le n-1, j \ne i$  $V \leftarrow V \cup \bigcup_{j=0}^{n-1} S_j$ **if** k = f+1**then**  $y \leftarrow \min(V)$

In the previous algorithm, which is based on an algorithm by Dolev and Strong, each processor maintains a set of the values it knows to exist in the system. Initially, the set contains only its own input. In later rounds the processor updates its set by joining it with the sets received from other processors. It then broadcasts any new additions to the set of all processors. This continues for f + 1 rounds, where f is the maximum number of processors that can fail. At this point, the processor decides on the smallest value in its set of values.

To prove the correctness of this algorithm we first notice that the algorithm requires exactly f + 1 rounds. This implies termination. Moreover the validity con-

#### 13.4. Fault-tolerant consensus

dition is clearly satisfied since the decision value is the input of some processor. It remains to show that the agreement condition holds. We prove the following lemma:

**Lemma 13.12** In every execution at the end of round f + 1,  $V_i = V_j$ , for every two nonfaulty processors  $p_i$  and  $p_j$ .

**Proof** We prove the claim by showing that if  $x \in V_i$  at the end of round f + 1 then  $x \in V_i$  at the end of round f + 1.

Let r be the first round in which x is added to  $V_i$  for any nonfaulty processor  $p_i$ . If x is initially in  $V_i$  let r = 0. If  $r \leq f$  then, in round  $r + 1 \leq f + 1$   $p_i$  sends x to each  $p_j$ , causing  $p_j$  to add x to  $V_j$ , if not already present.

Otherwise, suppose r = f + 1 and let  $p_j$  be a nonfaulty processor that receives x for the first time in round f + 1. Then there must be a chain of f + 1 processors  $p_{i_1}, \ldots p_{i_{f+1}}$  that transfers the value x to  $p_j$ . Hence  $p_{i_1}$  sends x to  $p_{i_2}$  in round one etc. until  $p_{i_{f+1}}$  sends x to  $p_j$  in round f + 1. But then  $p_{i_1}, \ldots, p_{i_{f+1}}$  is a chain of f + 1 processors. Hence at least one of them, say  $p_{i_k}$  must be nonfaulty. Hence  $p_{i_k}$  adds x to its set in round k - 1 < r, contradicting the minimality of r.

This lemma together with the before mentioned observations hence implies the following theorem.

**Theorem 13.13** The previous consensus algorithm solves the consensus problem in the presence of f crash failures in a message passing system in f + 1 rounds.

The following theorem was first proved by Fischer and Lynch for Byzantine failures. Dolev and Strong later extended it to crash failures. The theorem shows that the previous algorithm, assuming the given model, is optimal.

**Theorem 13.14** There is no algorithm which solves the consensus problem in less than f + 1 rounds in the presence of f crash failures, if  $n \ge f + 2$ .

What if failures are not benign? That is can the consensus problem be solved in the presence of *Byzantine* failures? And if so, how?

## 13.4.3. Consensus with Byzantine failures

In a computation step of a faulty processor in the Byzantine model, the new state of the processor and the message sent are completely unconstrained. As in the reliable case, every processor takes a computation step in every round and every message sent is delivered in that round. Hence a faulty processor can behave arbitrarily and even maliciously. For example, it could send different messages to different processors. It can even appear that the faulty processors coordinate with each other. A faulty processor can also mimic the behaviour of a crashed processor by failing to send any messages from some point on.

In this case, the definition of the consensus problem is the same as in the message passing model with crash failures. The validity condition in this model, however, is not equivalent with requiring that every nonfaulty decision value is the input of some processor. Like in the crash case, no conditions are put on the output of faulty processors.

# 13.4.4. Lower bound on the ratio of faulty processors

Pease, Shostak and Lamport first proved the following theorem.

**Theorem 13.15** In a system with n processors and f Byzantine processors, there is no algorithm which solves the consensus problem if  $n \leq 3f$ .

# 13.4.5. A polynomial algorithm

The following algorithm uses messages of constant size, takes 2(f + 1) rounds, and assumes that n > 4f. It was presented by Berman and Garay.

This consensus algorithm for Byzantine failures contains f + 1 phases, each taking two rounds. Each processor has a preferred decision for each phase, initially its input value. At the first round of each phase, processors send their preferences to each other. Let  $v_i^k$  be the majority value in the set of values received by processor  $p_i$  at the end of the first round of phase k. If no majority exists, a default value  $v_{\perp}$ is used. In the second round of the phase processor  $p_k$ , called the king of the phase, sends its majority value  $v_k^k$  to all processors. If  $p_i$  receives more than n/2 + f copies of  $v_i^k$  (in the first round of the phase) then it sets its preference for the next phase to be  $v_i^k$ ; otherwise it sets its preference to the phase kings preference,  $v_k^k$  received in the second round of the phase. After f + 1 phases, the processor decides on its preference. Each processor maintains a local array pref with n entries.

We prove correctness using the following lemmas. Termination is immediate. We next note the persistence of agreement:

**Lemma 13.16** If all nonfaulty processors prefer v at the beginning of phase k, then they all prefer v at the end of phase k, for all k,  $1 \le k \le f + 1$ .

**Proof** Since all nonfaulty processors prefer v at the beginning of phase k, they all receive at least n - f copies of v (including their own) in the first round of phase k. Since n > 4f, n - f > n/2 + f, implying that all nonfaulty processors will prefer v at the end of phase k.

#### CONSENSUS-WITH-BYZANTINE-FAILURES

Code for processor  $p_i$ ,  $0 \le i \le n-1$ . Initially  $pref[j] = v_{\perp}$ , for any  $j \ne i$ round 2k - 1,  $1 \le k \le f + 1$

- 1 send  $\langle pref[i] \rangle$  to all processors

- 2 receive  $\langle v_j \rangle$  from  $p_j$  and assign to pref[j], for all  $0 \leq j \leq n-1, j \neq i$

- 3 let maj be the majority value of  $pref[0], \ldots, pref[n-1](v_{\perp} \text{ if none})$

- 4 let *mult* be the multiplicity of *maj*

```

round 2k, 1 \leq k \leq f+1

5 if i = k

6

then send \langle maj \rangle to all processors

receive \langle king-maj \rangle from p_k (v_{\perp} if none)

7

if mult > \frac{n}{2} + f

8

9

then pref[i] \leftarrow maj

else pref[i] \leftarrow king - maj

10

if k = f + 1

11

12

then y \leftarrow pref[i]

```

This implies the validity condition: If they all start with the same input v they will continue to prefer v and finally decide on v in phase f+1. Agreement is achieved by the king breaking ties. Since each phase has a different king and there are f+1 phases, at least one round has a nonfaulty king.

**Lemma 13.17** Let g be a phase whose king  $p_g$  is nonfaulty. Then all nonfaulty processors finish phase g with the same preference.

**Proof** Suppose all nonfaulty processors use the majority value received from the king for their preference. Since the king is nonfaulty, it sends the same message and hence all the nonfaulty preferences are the same.

Suppose a nonfaulty processor  $p_i$  uses its own majority value v for its preference. Thus  $p_i$  receives more than n/2 + f messages for v in the first round of phase g. Hence every processor, including  $p_g$  receives more than n/2 messages for v in the first round of phase g and sets its majority value to v. Hence every nonfaulty processor has v for its preference.

Hence at phase g+1 all processors have the same preference and by Lemma 13.16 they will decide on the same value at the end of the algorithm. Hence the algorithm has the agreement property and solves consensus.

**Theorem 13.18** There exists an algorithm for n processors which solves the consensus problem in the presence of f Byzantine failures within 2(f+1) rounds using constant size messages, if n > 4f.

# 13.4.6. Impossibility in asynchronous systems

As shown before, the consensus problem can be solved in synchronous systems in the presence of both crash (benign) and Byzantine (severe) failures. What about asynchronous systems? Under the assumption that the communication system is completely reliable, and the only possible failures are caused by unreliable processors, it can be shown that if the system is completely asynchronous then there is no consensus algorithm even in the presence of only a single processor failure. The result holds even if the processors only fail by crashing. The impossibility proof relies heavily on the system being asynchronous. This result was first shown in a breakthrough paper by Fischer, Lynch and Paterson. It is one of the most influential results in distributed computing.

The impossibility holds for both shared memory systems if only read/write registers are used, and for message passing systems. The proof first shows it for shared memory systems. The result for message passing systems can then be obtained through simulation.

**Theorem 13.19** There is no consensus algorithm for a read/write asynchronous shared memory system that can tolerate even a single crash failure.

And through simulation the following assertion can be shown.

**Theorem 13.20** There is no algorithm for solving the consensus problem in an asynchronous message passing system with n processors, one of which may fail by crashing.

Note that these results do not mean that consensus can never be solved in asynchronous systems. Rather the results mean that there are no algorithms that guarantee termination, agreement, and validity, in all executions. It is reasonable to assume that agreement and validity are essential, that is, if a consensus algorithm terminates, then agreement and validity are guaranteed. In fact there are efficient and useful algorithms for the consensus problem that are not guaranteed to terminate in all executions. In practice this is often sufficient because the special conditions that cause non-termination may be quite rare. Additionally, since in many real systems one can make some timing assumption, it may not be necessary to provide a solution for asynchronous consensus.

## **Exercises**

**13.4-1** Prove the correctness of algorithm CONSENSUS-CRASH.

**13.4-2** Prove the correctness of the consensus algorithm in the presence of Byzantine failures.

**13.4-3** Prove Theorem **13.20**.

# 13.5. Logical time, causality, and consistent state

In a distributed system it is often useful to compute a global state that consists of the states of all processors. Having access to the global can allows us to reason about the system properties that depend on all processors, for example to be able to detect a deadlock. One may attempt to compute global state by stopping all processors, and then gathering their states to a central location. Such a method is will-suited for many distributed systems that must continue computation at all times. This section discusses how one can compute global state that is quite intuitive, yet consistent, in a precise sense. We first discuss a distributed algorithm that imposes a global order on instructions of processors. This algorithm creates the illusion of a global clock available to processors. Then we introduce the notion of one instruction causally affecting other instruction, and an algorithm for computing which instruction affects which. The notion turns out to be very useful in defining a consistent global state of distributed system. We close the section with distributed algorithms that compute a consistent global state of distributed system.

# 13.5.1. Logical time

The design of distributed algorithms is easier when processors have access to (Newtonian) global clock, because then each event that occurs in the distributed system can be labeled with the reading of the clock, processors agree on the ordering of any events, and this consensus can be used by algorithms to make decisions. However, construction of a global clock is difficult. There exist algorithms that approximate the ideal global clock by periodically synchronising drifting local hardware clocks. However, it is possible to totally order events without using hardware clocks. This idea is called the *logical clock*.

Recall that an execution is an interleaving of instructions of the n programs. Each instruction can be either a computational step of a processor, or sending a message, or receiving a message. Any instruction is performed at a distinct point of global time. However, the reading of the global clock is not available to processors. Our goal is to assign values of the logical clock to each instruction, so that these values appear to be readings of the global clock. That is, it possible to postpone or advance the instants when instructions are executed in such a way, that each instruction x that has been assigned a value  $t_x$  of the logical clock, is executed exactly at the instant  $t_x$  of the global clock, and that the resulting execution is a valid one, in the sense that it can actually occur when the algorithm is run with the modified delays.

The LOGICAL-CLOCK algorithm assigns logical time to each instruction. Each processor has a local variable called *counter*. This variable is initially zero and it gets incremented every time processor executes an instruction. Specifically, when a processor executes any instruction other than sending or receiving a message, the variable *counter* gets incremented by one. When a processor sends a message, it increments the variable by one, and attaches the resulting value to the message. When a processor receives a message, then the processor retrieves the value attached to the message, then calculates the maximum of the value and the current value of *counter*, increments the maximum by one, and assigns the result to the *counter* variable. Note that every time instruction is executed, the value of *counter* is incremented by at least one, and so it grows as processor keeps on executing instructions. The value of logical time assigned to instruction x is defined as the pair (*counter*, id), where *counter* is the value of the variable *counter* right after the instruction has been executed, and *id* is the identifier of the processor. The values of logical time form a total order, where pairs are compared lexicographically. This logical time is also called Lamport time. We define  $t_x$  to be a quotient counter + 1/(id+1), which is an equivalent way to represent the pair.

**Remark 13.21** For any execution, logical time satisfies three conditions: (i) if an instruction x is performed by a processor before an instruction y is performed by the same processor, then the logical time of x is strictly smaller than that of y, (ii) any two distinct instructions of any two processors get assigned different logical times, (iii) if instruction x sends a message and instruction y receives this message, then the logical time of x is strictly smaller than that of y.

Our goal now is to argue that logical clock provides to processors the illusion of global clock. Intuitively, the reason why such an illusion can be created is that we can take any execution of a deterministic algorithm, compute the logical time  $t_x$  of each instruction x, and run the execution again delaying or speeding up processors and messages in such a way that each instruction x is executed at the instant  $t_x$  of the global clock. Thus, without access to a hardware clock or other external measurements not captured in our model, the processors cannot distinguish the reading of logical clock from the reading of a real global clock. Formally, the reason why the re-timed sequence is a valid execution that is indistinguishable from the original execution, is summarised in the subsequent corollary that follows directly from Remark 13.21.

**Corollary 13.22** For any execution  $\alpha$ , let T be the assignment of logical time to instructions, and let  $\beta$  be the sequence of instructions ordered by their logical time in  $\alpha$ . Then for each processor, the subsequence of instructions executed by the processor in  $\alpha$  is the same as the subsequence in  $\beta$ . Moreover, each message is received in  $\beta$  after it is sent in  $\beta$ .

# 13.5.2. Causality

In a system execution, an instruction can affect another instruction by altering the state of the computation in which the second instruction executes. We say that one instruction can *causally* affect (or influence) another, if the information that one instruction produces can be passed on to the other instruction. Recall that in our model of distributed system, each instruction is executed at a distinct instant of global time, but processors do not have access to the reading of the global clock. Let us illustrate causality. If two instructions are executed by the same processor, then we could say that the instruction executed earlier can causally affect the instruction executed later, because it is possible that the result of executing the former instruction was used when the later instruction was executed. We stress the word possible, because in fact the later instruction may not use any information produced by the former. However, when defining causality, we simplify the problem of capturing how processors influence other processors, and focus on what is possible. If two instructions x and y are executed by two different processors, then we could say that instruction x can causally affect instruction y, when the processor that executes x sends a message when or after executing x, and the message is delivered before or during the execution of y at the other processor. It may also be the case that influence is passed on through intermediate processors or multiple instructions executed by processors, before reaching the second processor.

We will formally define the intuition that one instruction can causally affect another in terms of a relation called *happens before*, and that relates pairs of instructions. The relation is defined for a given execution, i.e., we fix a sequence of instructions executed by the algorithm and instances of global clock when the instructions were executed, and define which pairs of instructions are related by the

#### 13.5. Logical time, causality, and consistent state

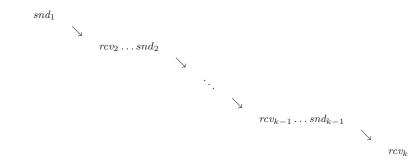

happens before relation. The relation is introduced in two steps. If instructions x and y are executed by the same processor, then we say that x happens before y if and only if x is executed before y. When x and y are executed by two different processors, then we say that x happens before y if and only if there is a chain of instructions and messages

for  $k \geq 2$ , such that  $snd_1$  is either equal to x or is executed after x by the same processor that executes x;  $rcv_k$  is either equal to y or is executed before y by the same processor that executes y;  $rcv_h$  is executed before  $snd_h$  by the same processor,  $2 \leq h < k$ ; and  $snd_h$  sends a message that is received by  $rcv_{h+1}$ ,  $1 \leq h < k$ . Note that no instruction happens before itself. We write  $x <_{HB} y$  when x happens before y. We omit the reference to the execution for which the relation is defined, because it will be clear from the context which execution we mean. We say that two instructions x and y are *concurrent* when neither  $x <_{HB} y$  nor  $y <_{HB} x$ . The question stands how processors can determine if one instruction happens before another in a given execution according to our definition. This question can be answered through a generalisation of the LOGICAL-CLOCK algorithm presented earlier. This generalisation is called vector clocks.

The VECTOR-CLOCKS algorithm allows processors to relate instructions, and this relation is exactly the happens before relation. Each processor  $p_i$  maintains a vector  $V_i$  of n integers. The j-th coordinate of the vector is denoted by  $V_i[j]$ . The vector is initialised to the zero vector  $(0, \ldots, 0)$ . A vector is modified each time processor executes an instruction, in a way similar to the way *counter* was modified in the LOGICAL-CLOCK algorithm. Specifically, when a processor  $p_i$  executes any instruction other than sending or receiving a message, the coordinate  $V_i[i]$  gets incremented by one, and other coordinates remain intact. When a processor sends a message, it increments  $V_i[i]$  by one, and attaches the resulting vector  $V_i$  to the message. When a processor  $p_j$  receives a message, then the processor retrieves the vector V attached to the message, calculates coordinatewise maximum of the current vector  $V_j$  and the vector V, except for coordinate  $V_i[j]$  that gets incremented by one, and assigns the result to the variable  $V_j$ .

$V_{j}[j] \leftarrow V_{j}[j] + 1$ for all  $k \in [n] \setminus \{j\}$  $V_{j}[k] \leftarrow \max\{V_{j}[k], V[k]\}$

#### 13. Distributed Algorithms

We label each instruction x executed by processor  $p_i$  with the value of the vector  $V_i$  right after the instruction has been executed. The label is denoted by VT(x) and is called *vector timestamp* of instruction x. Intuitively, VT(x) represents the knowledge of processor  $p_i$  about how many instructions each processor has executed at the moment when  $p_i$  has executed instruction x. This knowledge may be obsolete.

Vector timestamps can be used to order instructions that have been executed. Specifically, given two instructions x and y, and their vector timestamps VT(x) and VT(y), we write that  $x \leq_{VT} y$  when the vector VT(x) is majorised by the vector VT(y) i.e., for all k, the coordinate VT(x)[k] is at most the corresponding coordinate VT(y)[k]. We write  $x <_{VT} y$  when  $x \leq_{VT} y$  but  $VT(x) \neq VT(y)$ .

The next theorem explains that the VECTOR-CLOCKS algorithm indeed implements the happens before relation, because we can decide if two instructions happen or not before each other, just by comparing the vector timestamps of the instructions.

**Theorem 13.23** For any execution and any two instructions x and y,  $x <_{HB} y$  if and only if  $x <_{VT} y$ .

**Proof** We first show the forward implication. Suppose that  $x <_{HB} y$ . Hence x and y are two different instructions. If the two instructions are executed on the same processor, then x must be executed before y. Only finite number of instructions have been executed by the time y has been executed. The VECTOR-CLOCK algorithm increases a coordinate by one as it calculates vector timestamps of instructions from x until y inclusive, and no coordinate is ever decreased. Thus  $x <_{VT} y$ . If x and y were executed on different processors, then by the definition of happens before relation, there must be a finite chain of instructions and messages leading from x to y. But then by the VECTOR-CLOCK algorithm, the value of a coordinate of vector timestamp gets increased at each move, as we move along the chain, and so again  $x <_{VT} y$ .

Now we show the reverse implication. Suppose that it is not the case that  $x <_{HB}$ y. We consider a few subcases always concluding that it is not that case that  $x <_{yT} y$ . First, it could be the case that x and y are the same instruction. But then obviously vector clocks assigned to x and y are the same, and so it cannot be the case that  $x <_{VT} y$ . Let us, therefore, assume that x and y are different instructions. If they are executed by the same processor, then x cannot be executed before y, and so x is executed after y. Thus, by monotonicity of vector timestamps,  $y <_{VT} x$ , and so it is not the case that  $x <_{VT} y$ . The final subcase is when x and y are executed by two distinct processors  $p_i$  and  $p_j$ . Let us focus on the component i of vector clock  $V_i$  of processor  $p_i$  right after x was executed. Let its value be k. Recall that other processors can only increase the value of their components i by adopting the value sent by other processors. Hence, in order for the value of component i of processor  $p_i$ to be k or more at the moment y is executed, there must be a chain of instructions and messages that passes a value at least k, originating at processor  $p_i$ . This chain starts at x or at an instruction executed by  $p_i$  subsequent to x. But the existence of such chain would imply that x happens before y, which we assumed was not the case. So the component i of vector clock VT(y) is strictly smaller than the component i of vector clock VT(x). Thus it cannot be the case that  $x <_{_{VT}} y$ .

This theorem tells us that we can decide if two distinct instructions x and y are concurrent, by checking that it is not the case that VT(x) < VT(y) nor is it the case that VT(x) > VT(y).

## 13.5.3. Consistent state